DDR-SDRAMと言えばもはや皆が知っている部品となっていますが、エンジニア視点で、DDR-SDRAMとは何かを解説していこうと思います、仕組み、動作、世代間の違い、物理層評価のポイント、オシロスコープでの測定方法と、注意点。エンジニアに必要な内容を一通りまとめたいと思いますので、参考にしていただければ幸いです。

DDR-SDRAMとは

DDR-SDRAMとは

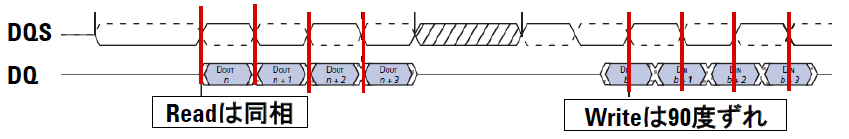

Double Data Rate-SDRAMの略で、クロック周波数の2倍のデータ転送レートが得られるSDRAMです。

データ送信側がストローブ信号(DQS)を出力。

データ受信側はDQSの両エッジで信号をラッチします。

イメージ図は下記です。

※DQ: Data Queue DQS: Data Queue Strobe

では、SDRAMとはなんでしょうか?

Synchronous DRAMの略で、クロック同期で動作するメモリで、システムクロックにメモリクロックを同期させる事で、お互いの制御を容易にするという発想で生まれたDRAMです。

ではDRAMとは何でしょうか?

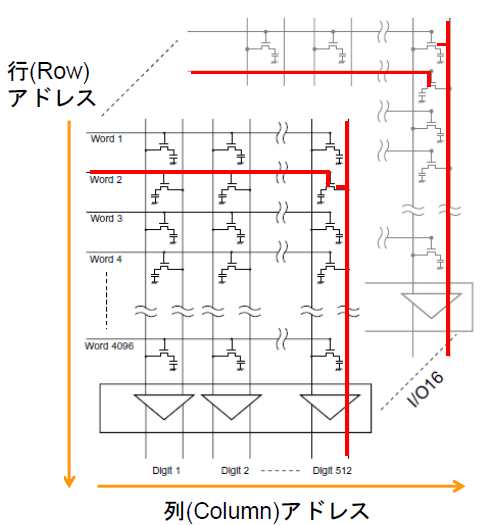

Dynamic Random Access Memoryの略で、行と列を指定してデータのリード/ライトを実施できるメモリ。放っておくと電荷が漏れてデータが消える。またデータを読み出すとデータが消える、電荷の有無で0/1を判断、1bitにつきコンデンサが1個ついているメモリです。

DRAMの中身のイメージは次のようになっています。

DDR-SDRAMの信号

■コマンド信号

- CK: 動作クロック

- /RAS,/CAS,/WE: この3つの信号の組み合わせでコマンド決定

- CKE: クロック・イネーブル

- VDD,VDDQ,Vref,VDDL: 各種供給電源

- VSS,VSSQ,VSSDL: 各種GND

- ODT: On-Die Termination DRAM内部の終端抵抗

- ZQ: ZQキャリブレーションで使用

■アドレス信号

- A0~A15: メモリのアドレス指定に使用

- /CS: チップセレクト、複数のDRAMが同じデータ線を共有する場合、チップを選択する為使用

- BA0~: Bank Address Bankの指定に使用

■データ信号

- DQ0~: データ線。x8なら8本、x16なら16本

- DQS: DQ(データ)用のクロック、ストローブ信号、DQ8本に対し、DQSが1本割り当てられている。

- DM: Data Mask。DMがHighの時だけDQのデータが有効

DDR 世代間の違い

- DDR1

- 200~400Mbps

- Double Data Rate:クロック周波数の2倍の転送レート

- 差動クロック:高速化やノイズに対応

- Data Strobe(DQS):クロックと同周期の信号、データの入出力はDQSの両エッジに同期

- DLL回路の採用:内部と外部クロック時間差を制御、調整

- 電源電圧2.5V

- DDR2

- 400~800Mbps

- On-Die Termination(ODT):DRAM内部に終端抵抗、反射低減

- Off-Chip Driver:出力ドライバのインピーダンス調整

- 差動DQS

- 電源電圧1.8V

- DDR3

- 800~1600Mbps

- Dynamic ODT:ODTの終端抵抗を自己補正

- アドレス、コマンドの配線がFly-byトポロジ

- 電源電圧1.5V Vref:VDDの1/2

- DDR4

- 1600~3200Mbps

- DBI(Data Bus Inversion)などによる消費電力削減

- CRCなどによる信頼性の向上

- 電源電圧1.2V VPP:2.5V(Vref生成用)

DDR伝送方式の特徴

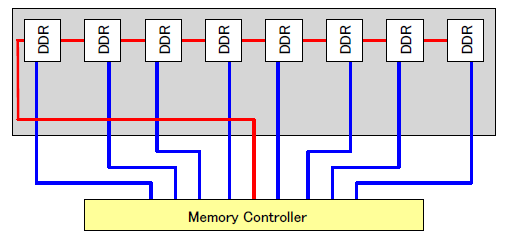

■トポロジ―

DDR2まで:トーナメント方式(下図)

赤(T-Branch):Clock, Address, Command

青線(Point to Point):DQ, DQS

※課題:T-Branchはインピーダンスの整合が難しく、高速になると波形品質に問題がでる。

DDR3以降:フライバイ方式(下図)

赤(Fly-By):Clock, Address, Command

青線(Point to Point):DQ, DQS

※課題:DQ信号とCMD,Address,Clock信号との間にFlight Timeの差ができるので、コントローラはそれぞれの信号を送出するタイミングを調整する必要がある。

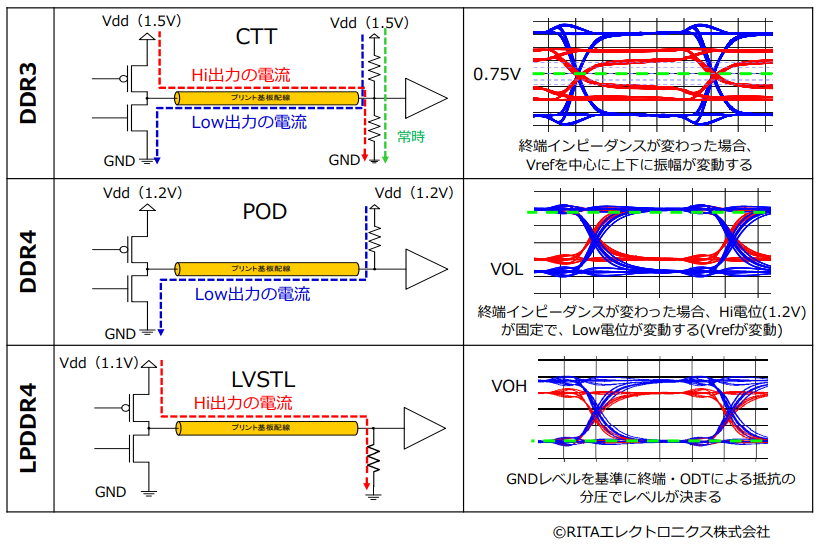

■伝送方式

DDR3及びDDR4での伝送方式の差は下の図のようになります。電流の流れに着目して頂けると分かりますが、DDR3に関しては、Hi/Lowどちらにおいても電流が流れるような伝送仕様となっておりますが、DDR4はLow出力の時のみ、LPDDR4はHi出力の時のみとなっており、DDR3に比べ、DDR4の方が消費電流が抑えられる仕様になっている事が分かると思います。

DDR物理層評価のポイントとオシロスコープでの測定方法

オシロスコープを用いて、DDR周りの信号の測定を実施する際は注意が必要です。もちろん測定する周波数帯域に見合ったオシロスコープを使う必要がありますが、機材とは別に測定ポイントが重要になります。低速の信号ライン、例えばI2C,SPI,UARTといった信号線を測定する場合は、測定できればどのポイントでも良かったのですが、DDRのような高速信号になると、測定するポイント(場所)により、反射波が見えてしまい、実際の波形の測定が出来なくなる、という恐れがあります。

つまり、オシロで測定する場合は、各信号その受信端で測定する必要があり、そこで測定しないと、正確な波形が分からない。という事になります。

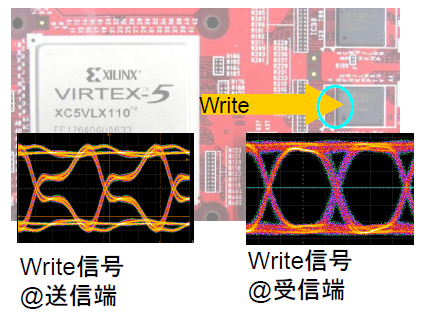

1例を下に示します。下の例はDDR3の波形ですが、ホスト(下の場合Virtex-5)からDDR3へ書き込みを行った時のWrite信号です。送信端と受信端の波形はこの図ように違いがあります。送信端の波形が乱れている原因は、受信端のデバイスから跳ね返ってきた反射波がある為にこういった波形になります。ではこの波形はOKなのか、NGなのかどちらなのでしょうか?

もちろん判定は受信端で実施する必要があるので、〇となりますが、もし送信端でしか測定しなかった場合、✖という判定を誤ってしてしまうかもしれません。また、送信端の波形を〇にする事が出来るかというと、とても難しいです。理由はデバイスの受信端で必ずインピーダンスの不整合が発生する為、必ずその反射波が返ってくるためです。

この事を知らずに、通常の低速ラインと同じ測定方法を行うと必ずハマりますのでご注意ください。

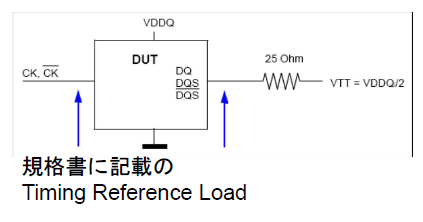

ちなみにJEDECの規格書にも測定ポイントは受信端で測定するようにと記載があります。↓

それでは、受信端で測定する為にはどうしたらよいでしょう?それには2つの方法があります。

- 基板表層に配線されている場合は、レジストを剥がしてプローブポイントとする。もしくは、基板作成時にあらかじめ受信端のレジストはつけない。裏面からスルーホールを通してピンへ接続されている場合、スルーホール部分のレジストをつけず、そこで測定する。

この場合は、基板表層(裏表)に測定する通信ラインが通っている場合に限ります。一番してはいけない事は、本来内層を走っている配線を測定する為に、わざわざ配線を内層から表層に引っ張り出しテスト用のランドを設ける事です。それをする事で、トポロジーも変わってしまい、テストパットを出す事が原因で波形品質を劣化させてしまいます。

また、表層に走っている配線においても、テストパットを配置するのではなく、レジストを剥がすだけにしておく必要があります。テストパットの形状は通常の配線幅より広く、そこでインピーダンスの不整合が発生してしまい、トポロジーが変わってしまいます。

測定の為にトポロジーを変える事は絶対にNGです。

それでは、内層を配線が通っている場合はどうすれば良いでしょうか?その場合は次の測定方法を実施します。

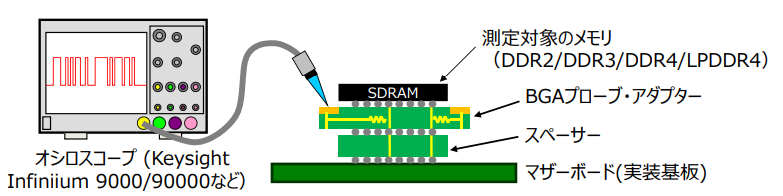

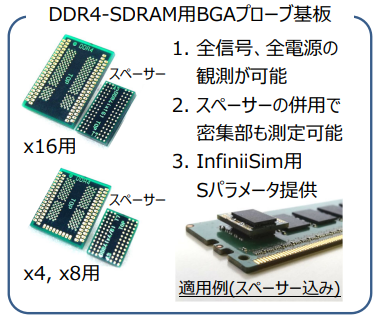

- 別売のプローブアダプタやスペーサを用いる

DDRの波形測定を実施する場合、この方法がメジャーな方法かつ、正しく測定できる方法だと思います。イメージは下記。実装基板とメモリの間にプローブアダプタとスペーサを入れる事で、このアダプター上で測定するという方法です。

実際の基板は↓のようなイメージ

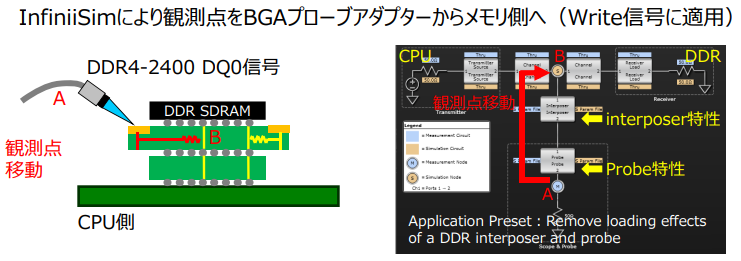

この図だけ見ると、トポロジーがかわってしまうと思われるかもしれませんが、 各通信ラインに関してはインピーダンスコントロールがしっかりなされており、反射等は発生されないように設計されております。かつ、測定においては、本基板のSパラメータが提供される事によって、基板測定ポイントとDDRのランド間の特性のギャップをキャンセルする事が可能な設計となっております。これはKeysightのオシロスコープとInfiniSimというソフトウェアとの組み合わせにより実現が可能となります。

イメージは下図の通りです、左の図のAとBの点が右のInfiniSim上でも表れており、プローブの特性、インターポーザ基板(BGAプローブアダプタ)をキャンセルし、B(DDRのランド部)の部分の波形をオシロに表示させる事が可能となります。

これを実施する事で、受信端の測定を正しく実施する事が可能となります。

動画でも解説しておりますので、よろしかったらご覧ください。

これまで説明させて頂いたDDRを扱う基板を設計する上で、基板のパターン設計、EMC対策は必須です。下記に高速配線のパターン設計の方法対策に関しての記事も書いておりますので、よろしければ、ご参考にしていただければ幸いです。

【高速信号配線&基板ノイズ対策】プリント基板のパターン設計ノウハウ集

ノイズとの闘い。ものづくりエンジニアの為の、EMCとは?EMC設計技術とは?

その他高速伝送路の記事は下記も参照いただければ幸いです。

参考:USB3.xとUSB2.0の違いをエンジニア視点で解説します。

参考:差動伝送規格、LVDSとは?誤解されがちな規格とメリットを徹底解説

エンジニアになる為のブログラムの学習は下記から。

参考:収入アップの為の、おすすめプログラミングスクール3社を紹介します

記事が気に入って頂けたら、クリックして頂けると嬉しいです。

コメント