始めてCMOSイメージセンサを使ったカメラを設計される電気設計者の為に、CMOSイメージャの周辺回路設計をする時の注意事項を実例も含めて記載していきたいと思います。

CMOSイメージャは、いろいろなメーカから出ています。ソニー、オムニビジョン、オンセミコンダクタが主な企業かと思いますが、周辺回路を設計する時の注意点は概ね同じです。

本記事ではWebで参考回路が見つけられたオンセミコンダクタのCMOSイメージャを例にとり、電気設計者の為に回路設計の仕方をお伝えしていきたいと思います。

抵抗や、コンデンサの基本的な使い方を始めに学びたい。という方は下記の記事も参照頂ければ幸いです。

【超実践編】エンジニアの為の、電子機器で使われる、抵抗器の役割6選

【超実践編】エンジニアの為の、電子機器で使われる、コンデンサの役割6選

CMOSイメージセンサの回路

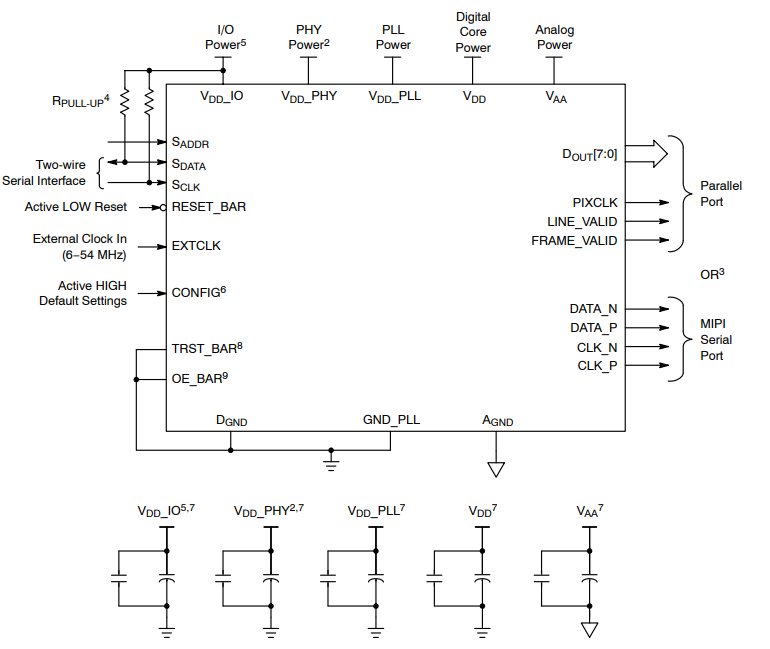

下の図が仕様書に乗っている参考回路です。1つ1つ解説していきたいと思います。この回路図はオンセミコンダクタの「MT9M114」という型番の1.26MピクセルサイズのCMOSイメージセンサです。

※一例として 「MT9M114」 を取り上げていますが、回路構成としては、どのイメージャも概ね同じです。

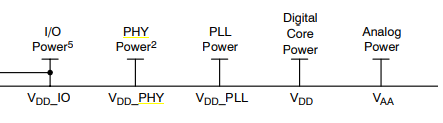

電源

まずは電源からです。電源は大きく分けて、「デジタル電源」「アナログ電源」の2つがイメージャにはあります。今回のイメージャを例にとると、次のようになります。

電源設計で最も重要な事は、デジタル電源とアナログ電源を分離する事です。また、アナログ電源はLDO等を用いて、リップルが発生しない電源を使う事は必須です。DCDCコンバータのようなスイッチング電源を使うと、リップルがそのままイメージャのアナログ回路に供給されるため、結果そのノイズがそのまま画像として現れてきます。それを回避する為には、リップルの発生しない電源、つまりLDOを用いてアナログ電源をつくる事を推奨いたします。

また、電源は立ち上げの順番が仕様書に記載されていますので、立ち上げ順番は守るように設計する必要があります。

■デジタル電源

- Digital Core Power 1.7-1.95V

- コア電源です、typ1.8VのDCDCまたは、LDOの電源供給で良いと思います。

- PLL Power 2.5-3.1V

- PLL(位相同期回路)つまりクロックを生成する回路です。typ2.8VのDCDCまたは、LDOの電源供給で良いと思います。

- PHY Power 1.7-1.95V

- MIPI駆動時のD-PHY駆動電源。typ1.8VのDCDCまたは、LDOの電源供給で良いと思います。D-PHYに関しては次に記事を参照頂ければ幸いです。

- ->MIPI CSI-2 の概要、カメラ開発のものづくりエンジニア必見。

- I/O Power 1.7-1.95 or 2.5-3.1V

- Interface回路の電源。主にはI2C通信時のIO電源となります。typ1.8Vもしくは2.8Vで、接続先のマイコンの電圧と共通電源にするのが良いと思います。

■アナログ電源

- Analog Power 2.5-3.1V

- typ2.8VのLDOで生成し、上記デジタル電源とは分離しましょう。

上記デジタル電源を準備する時、全系統分離できればよいですが、製品をつくる時は、基板のサイズ制約で、部品を減らす事が求められると思います。そういった制約がある時は、同じ電圧は1つの電源を使って供給する事も可能です。具体的にはCore電源とPHY電源は共通化可能です。その際はLCフィルタで分離しましょう。

各電源へはバイパスコンデンサ(パスコン)が必要です。こちらも基板サイズとの相談ですが、理想的にはイメージセンサ端子直近へは0.1uFをつけ、少し離れた所には1uFをつける。もしくはコンデンサの数を減らしたい場合は、3端子コンデンサを活用するという方法で、実装面積の削減をします。

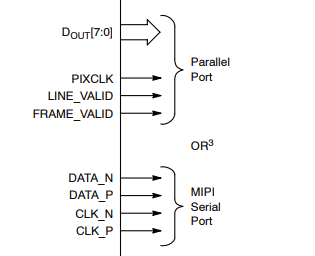

デジタルパラレル出力/MIPI出力

本イメージャの場合、データ出力は、デジタルパラレル出力とMIPI出力の2系統がありますので、それぞれについて説明したいと思います。

■デジタルパラレル出力

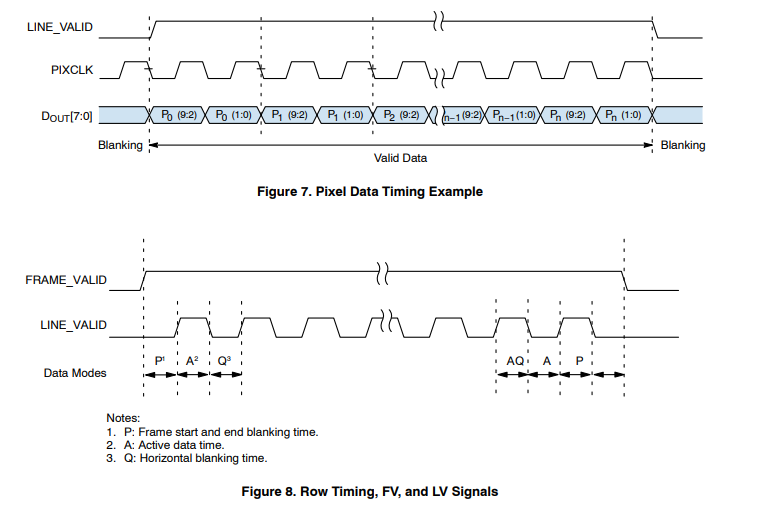

デジタルパラレル出力とは、例えば、8bitであれば、8個の端子からデータが一斉に出力される仕様であり、つまり1バイトのデータが同じタイミングで出力されるフォーマットです。その時にただ単純にデータだけを出力していては、それを受ける側のマイコンやISPが、この信号が映像データの中のどの信号なのか認識できない為、クロック、Vsync、Hsyncという信号がすべて同期して出力されます。このように、VsyncやHsyncがあるのは、下の記事に記載したように、イメージャの画素はすべて有効な映像信号で構成されているわけではない為、これらの信号を使って、有効が映像がどこからどこまでで、今何ライン目の映像を流しているのかを通知する仕組みとなっています。

- クロック

- データ出力の基準となる信号です。このクロックに同期し、Hsync、Vsync、データは出力されます。

- Vsync

- フレーム(有効な映像信号)を通知する為の信号。本仕様書では「FRAME_VALID」という名前になっていますが、意味合いは同じで、出力されているデータのフレームを通知する為の信号です。

- Hsync

- 有効な映像信号のラインを通知する為の信号。本仕様書では「LINE_VALID」という名前になっていますが、意味は同じで、出力されているデータの各ラインを通知する為の信号です。

- データ

- 各ピクセルの画像データを出力

波形の参考は下記の通りです。

これらのラインに対する回路は、ダンピング抵抗を直列に着けておく程度で問題ありません。また、ダンピング抵抗は、出力側に近い所に配置した方が効果的である為、イメージャ近くに配置するようにしましょう。

■MIPI出力

MIPIに関しては、下記記事で詳しく記載していますので、参考にしていただければ幸いですが、回路という意味で重要な事は、差動インピーダンス100Ωで版下設計をする事や、高速配線の配線ルールをしっかり守って配線する事です。どんな配線にすべきかは、「【高速信号配線&基板ノイズ対策】プリント基板のパターン設計ノウハウ集」を参考にしていただけると幸いです。

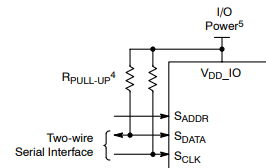

I2C通信

イメージャ内の各種レジスタの設定をする為に、古くからI2C通信が使われています。非常に簡単な通信であり、SCLと呼ばれるクロック信号と、SDAと呼ばれるデータの2本で通信を実施します。回路としては、IO電源に対してプルアップする必要があり、それぞれのイメージャのドライブ能力に依存しますが、仕様書に記載ある抵抗値の抵抗でプルアップしておけば問題ないと思います。本参考回路では、1.5kΩでプルアップするように記載がありますので、それに従う事になります。

I2C通信は、デイジーチェーンといって、複数のデバイスを、1本のI2Cバス(SCKとSDA)で接続が可能というところにメリットがあります。デバイスごとに個別に配線をする必要が無い為、基板上の配線の面積という意味で有利な通信規格となります。ただし、このように複数のデバイスが1本の通信ラインで接続される為、ホストがどのデバイスに通信をしているか分かるようにする為、各デバイスに、「スレーブアドレス」という番号が付けられます。

各デバイスごとにスレーブアドレスが付いているのですが、もし同じデバイスを2個搭載した場合にこのスレーブアドレスが固定されていては、識別できなくなってしまうため、イメージャにはスレーブアドレスを変更する為の端子が付けられている場合が多く、この端子を使ってスレーブアドレスを選択できるようになっている場合が多いです。

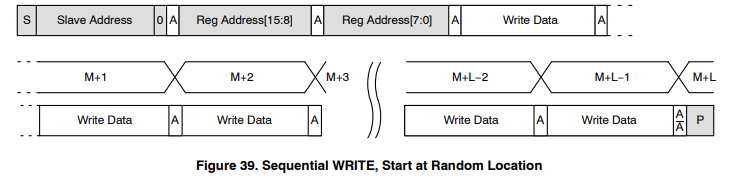

データ書き込みのシーケンス例を次に示します。スタートビットで送信開始を通知して、スレーブアドレスで送信相手を指定、その後は、データの送信とAck(応答)でハンドシェイクする事で通信を行います。

■I2Cデータ送受信例

- 【Master(ホスト)→Slave(イメージャ)】スタートビット(SDAをHigh→Lowへ下げる)

- 【Master(ホスト)→Slave(イメージャ)】スレーブアドレス送信

- 【Slave(イメージャ)→ Master(ホスト)】Ackの送信(SDAをLowへする事でAck通知)

- 【Master(ホスト)→Slave(イメージャ)】アドレスの送信

- 【Slave(イメージャ)→ Master(ホスト)】Ackの送信(SDAをLowへする事でAck通知)

- 【Master(ホスト)→Slave(イメージャ)】書き込みデータの送信の送信

- 【Slave(イメージャ)→ Master(ホスト)】Ackの送信(SDAをLowへする事でAck通知)

マスタークロック入力

イメージャを駆動させるためのマスタークロックです。イメージャのすべての動作がこのマスタークロックに同期して動く事になりますので、非常に重要なクロックです。通常は、発振器をイメージャのすぐ近くに配置して、クロックの配線は最短に配線する事で信号品質の担保を行います。配線ルールは、 「【高速信号配線&基板ノイズ対策】プリント基板のパターン設計ノウハウ集」 を守って頂ければ問題ありません。このクロックへも、出力端子近くにはダンピング抵抗をつけ、変なオーバーシュートやアンダーシュートが出ない様にケアする必要があります。

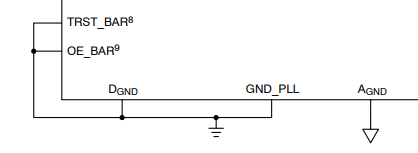

GND

GNDは基本ベタGNDとする事を推奨しますが、アナログGNDとデジタルGNDの分離をする必要があるかないか、というのが、いつもイメージャの回路設計では話題になる所かと思います。本参考回路では、アナログGNDとデジタルGNDを分けるように、指示されています。

しかしながら、実際カメラモジュールの設計をされている方、非常に小さい製品設計をしなければいけない中で、GNDをアナログとデジタルの2つを完全に独立させる事が出来るでしょうか?

難しいと思います。

もし基板に十分な面積があれば、GNDを分ける事に越したことはないですが、実際のものづくりの現場では、難しい場合が多く、GNDは接続せざるをえない場合が多いと思います。その場合は、ベタで接続するのではなく、1点アースという考え方で接続しましょう。つまり、アナログGNDの島はしっかりアナログ電源と対に形成し、リターンパスは出来るだけその島を通じて戻ってくるように設計しますが、そのアナログGNDの島は、どこか一点でデジタルGNDの大きなベタGNDと接続するという、配線方法です。そうする事で、物理的には接続された共通GNDとはなりますが、デジタルのノイズがアナログラインに入りにくくなる(その逆もしかり)と同時に、配線の自由度も上がりますので、試していただけると幸いです。

まとめ

始めてCMOSイメージセンサを使ったカメラを設計される電気設計者の為に、CMOSイメージャの周辺回路設計をする時の注意事項をまとめてきました。イメージャの回路設計は回路という意味では簡単ですが、アナログ電源と、MIPIを扱う場合はMIPIのライン、この2つのケアが必要です、アナログ電源をミスすると画像が横筋だらけで見られなくなってしまいますし、MIPIのラインをミスすると、映像そのものが出なくなります。

ただ、逆にいうとこの2点だけ抑えておけば誰でもイメージャを使う基板の電気設計が出来ますので、もし機会があれば、チャレンジされてはいかがでしょうか。

動画でも解説しておりますので、よろしかったらご覧ください。

記事が気に入って頂けたら、クリックして頂けると嬉しいです。

コメント

はじめまして、「科学・学びブログ天紹介所」管理人トミと申します。

是非ブログを当サイトで紹介させていただきたく参りました。

文字のみでは難しいゆえ、詳細URLからご閲覧いただければと存じます。

詳細ページ:https://www.tomiwato.com/blogrotate/00010science/mutual_description?site=339

ご検討のほどよろしくお願いします。

「科学・学びブログ天紹介所」管理人トミ様

コメントありがとうございます。

はい。ご連絡頂いた件、もちろん問題ありませんので、是非紹介いただきたいと思います。

よろしくお願いいたします。

アナログ電源をミスすると画像が横筋

まさに今このような状態に陥っており、可能であれば撮像した画像を見て頂き、記載している横筋なのか見て頂くことは可能でしょうか。

コメントありがとうございます。下記、ご参考になれば幸いです。

外部からのなんらかのノイズが印可される事により同じような横筋が出る事もありますので、画像だけでは一概にアナログ電源だけの起因である事が分からないですが、横筋が画面上から下へ流れるように現れていたり、イメージセンサのアナログゲインを上げると見えやすくなるような現象であれば可能性が高いと思われます。アナログ電源をもしDCDCコンバータで生成している場合は、より可能性が高いと思われますので、一度オシロで測定してリップルが出ているかどうかを確認される事をお勧めいたします!