LVDSの技術はシリアルインターフェイスの歴史を切り開いたといっても過言ではありません。ただし、誤解されやすく、差動伝送=LVDSと認識されがちです。差動伝送には有名なUSBやHDML,MIPIといった多くの種類がありますが、これらはすべてLVDS規格の信号ではありません。

本記事では、LVDSとな何か?その規格と、主に設計者が必要とする、振幅、速度、特性インピーダンスについて解説し、難しい規格書を読まなくても分かるように、LVDSというのは何なのか、そのメリットを解説していきたいと思います。

LVDSとは?

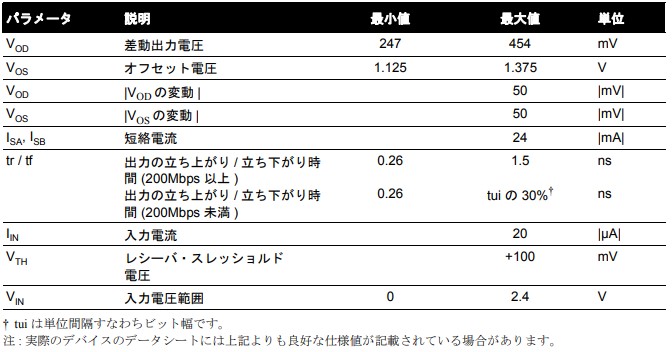

3.5mAの定電流で駆動し、100Ωの終端時に350mAの振幅でデータを転送する、差動シリアルインターフェイス。最高データレートは3.125Gbps。 それがLVDSです。

本記事で言いたい事は上記に集約されているのですが、ポイントは電流駆動である事。差動インピーダンス100Ωでコントロールされた伝送路のレシーバ端の100Ωの終端抵抗により、振幅は必然的に350mV(V=100Ω*3.5mA)になる。というところが特徴で、電圧駆動ではない。という事です。

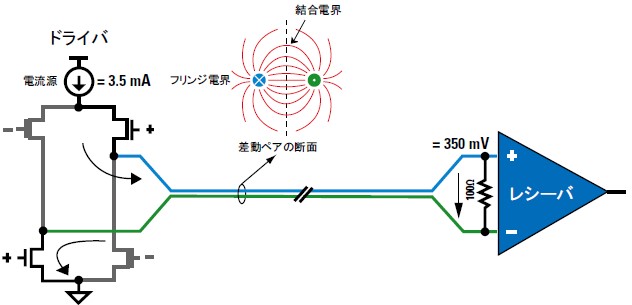

ドライバとレシーバのイメージは下記。ドライバは3.5mAの電流を流しその電流が青いラインを流れ、100Ω終端を通り、緑のラインで戻ってくる。これが、LVDSの電気の流れです。

また、コモンモード電圧(オフセット電圧)は1.2Vである為、1.2Vを中心に350mVの振幅をするというのが特徴です。

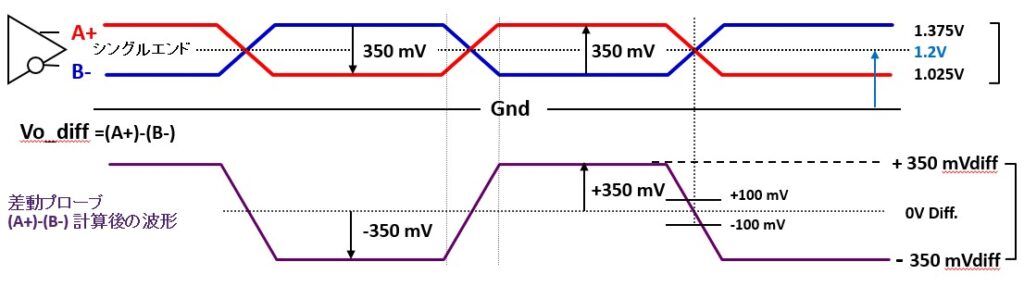

一方レシーバ側は入力電圧範囲が0~2.4Vと規格化されているため、その間の範囲で、受ける事が可能です。規格書に書かれている、仕様一覧は下記の通りです。

LVDS伝送のメリット

それでは、LVDSのメリットを解説する前に過去のパラレルインターフェイスの問題点を解説していきます。

■パラレルインターフェイスの課題

- 伝送データの増大により、パラレル配線の配線量が増加

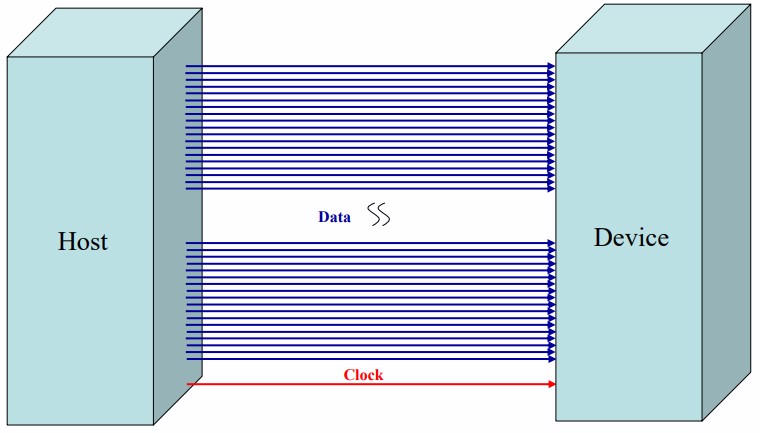

イメージは下記です。パラレルの本数がどんどんと増え、結果的に基板に配線する配線本数が増加、結果基板が大きくなる事を抑え、小型化しようとすると、配線が厳しい為、同一トポロジで配線できなくなる。結果、以下次の課題が発生する。

- 配線数の増加、伝送スピードの増加に伴い、各チャンネルごとのタイミングマージンが減少

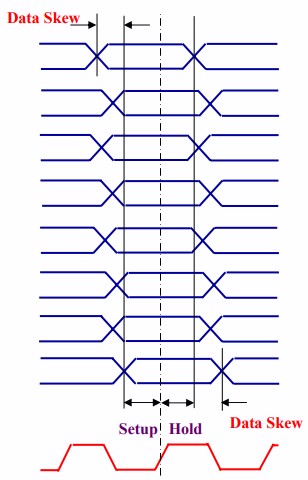

下の図のように、基本的に、伝送する際にはクロックの立ち上がり、もしくは立下り時のデータを読むという動作をするのですが、データのバス幅が広くなると、様々な理由で、時間のズレが生じます。それをSkew(スキュー)と言います。出力ドライバのバラつきや、伝送路のトポロジ(配線長等)の違いが主な原因です。

- 複数のパラレル信号の同時スイッチングによる、ノイズの増加

パラレルバスの信号が同時にスイッチするようなタイミングでノイズが発生します。例えば64bitバス、振幅3Vのパラレルバスで、64bitの信号が同時にHigh,Lowをした時に電圧、電流とも急激な変化をする為、GNDを揺らしたり、そのスイッチングノイズが放射したりと、EMC観点では非常に問題が発生します。ノイズに関しては下記のも参照頂ければ幸いです。

参考:ノイズとの闘い。ものづくりエンジニアの為の、EMCとは?EMC設計技術とは?

これらの課題を解決する為に、LVDSというシリアル伝送の方式が生まれました。LVDSの略は下記の通りであり、低電圧の差動信号による、シリアル通信で、上記のパラレルの課題を解決します。

LVDS : Low Voltage Differential Signaling

■LVDSのメリット

- メリット1:低電圧であること

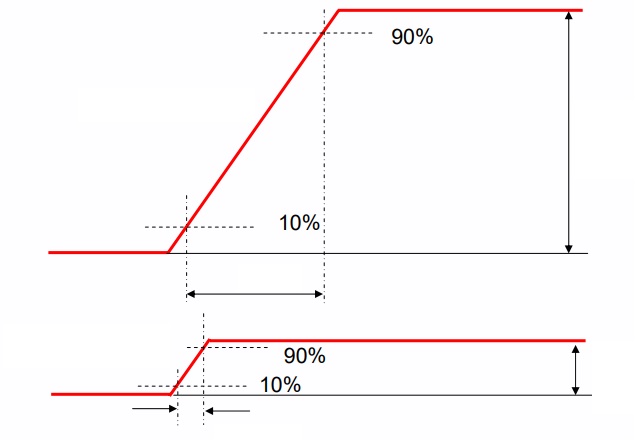

1つ目のメリットは低電圧である事です。電子回路の中で、電気の信号をデジタル値として、1,0を認識するに当たって、その中間電圧というのは必要ありません。しかしながら、電圧を0→3.3Vといったように、電圧を立ち上げる為には時間がかかります。一般的に受信側のデバイスは、例えば3.3VのCMOSインターフェイスを持っているとすると、約80%~90%の電圧以上をHighと認識し、10~20%以下の電圧をLowと認識、その間の電圧は不定電圧として扱われます(Highと認識されるか、Lowと認識されるか分からない)よって、0Vから3.3Vの90%である3.0Vまで出来るだけ早く立ち上げる必要がありますが、早ければ早いほどオーバーシュートといったノイズが出てきます。

つまり、高い電圧を持つインターフェイスで高速にHigh,Lowを繰り返す事は製品を設計するという観点では実際不可能です。その為、電圧のレベルを低く設定する事で、立ち上がりの速度は同じであっても、Highと認識出来るまでの速度を簡単に早くすることが出来、結果高速にHigh,Lowを繰り返す事が可能となります。

イメージは下の図の通りであり、電圧が低い下の図の方が、立ち上がりの速度(スリューレートという)が同じで合っても、Highと認識するまでの速度が速くなります。

ではなぜ、パラレル伝送時で電圧を低くしないのでしょうか?これはメリットの2につながる話ですが、電圧を低くするとノイズの影響を受けやすくなります。ちょっとしたノイズで波形が乱れ、それが原因で0,1の判断を誤る。という事が発生してしまうため、簡単に電圧だけを下げて高速伝送するという事はできません。

■メリット2:差動伝送である事

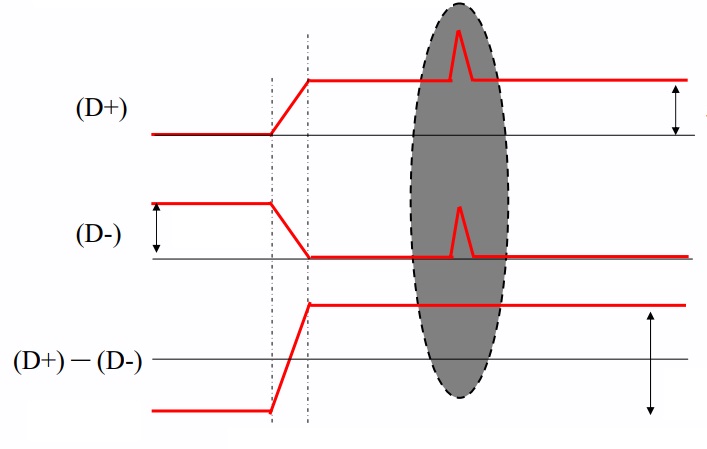

差動伝送である為、同一位相のノイズをキャンセルする事が可能。このメリットがとても大きく、これが出来る為に、低電圧化、高速化が可能となります。差動信号は単に2本の配線で伝送しているのではなく、受信側は+の信号とーの信号を合成した物を1つのデータとして受け取るという事をしています。

イメージは下の図ですが、D+の信号とDーの±の信号を合成した(D+)-(D-)という演算をレシーバはするのですが、この時、D+、D-に乗っている同一位相のノイズは、演算の結果消す事が出来る。という特徴があります。外部ノイズは基本的には同一タイミングで発生し、発生の仕方も全信号同一の出方をする場合が多いですが、そういったノイズはすべてキャンセルする事が出来ます。それが差動信号の最大の強みです。

■メリット3:ノイズを発生させない。

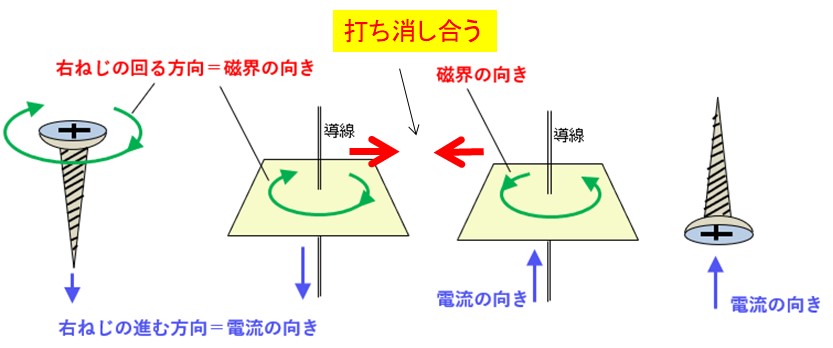

メリットの3つめは、ノイズの発生を抑制する事が出来る。という事です。原理は簡単で、昔習った右ネジの法則を覚えていますでしょうか?電流が流れると、その周りに右ネジの法則に従い磁界が発生するという物です。LVDSの信号は上で説明したように、電流駆動であり、その流れはドライバ→レシーバ→ドライバと戻ってきます。つまり、2本の配線の電流の流れは逆を向いています。それに右ネジの法則を用いると、2つの差動信号から発生する磁界は打ち消す方向に働く為、ノイズが発生しない。という原理です。下図。

まとめ

LVDSに関して説明しました。単に2本の配線で、逆位相なっているだけの信号ではなく、時代の進化と共に必然的に生まれて来た規格だと思います。製品設計をする上で、苦しんでいるノイズ、データの大容量化、基板の小型化、これらが従来の規格では対応できなくなるタイミングで生まれ、このLVDSに類似の差動伝送の規格が多く世の中には存在しています。そしてこの伝送規格で対応できないような進化が起こる時、次の世代の伝送規格が現れると思います。

その他高速伝送路の記事は下記も参照いただければ幸いです。

参考:USB3.xとUSB2.0の違いをエンジニア視点で解説します。

参考:車載用高速伝送ソニーのGVIFとは、FPD-LINKやGMSLも合わせて解説

参考:DDR-SDRAMとは、仕組み、動作、オシロスコープでの測定方法の解説

参考:MIPI D-PHY徹底解説、カメラ開発のものづくりエンジニア必見

参考:MIPI CSI-2 の概要、カメラ開発のものづくりエンジニア必見。

動画もありますので、よろしかったらご覧ください。

エンジニアになる為のブログラムの学習は下記から。

参考:収入アップの為の、おすすめプログラミングスクール3社を紹介します

記事が気に入って頂けたら、クリックして頂けると嬉しいです。

コメント